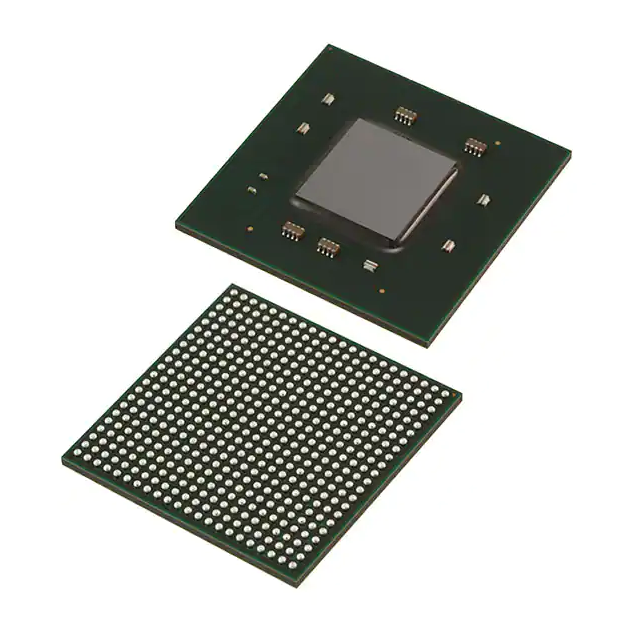

नवीन आणि मूळ XC7A100T-2FGG484I IC इंटिग्रेटेड सर्किट FPGA फील्ड प्रोग्रामेबल गेट ॲरे ad8313 IC FPGA 285 I/O 484FBGA

उत्पादन गुणधर्म

| TYPE | वर्णन |

| श्रेणी | एकात्मिक सर्किट्स (ICs)एम्बेडेड |

| Mfr | AMD Xilinx |

| मालिका | आर्टिक्स-7 |

| पॅकेज | ट्रे |

| मानक पॅकेज | 60 |

| उत्पादन स्थिती | सक्रिय |

| LABs/CLB ची संख्या | ७९२५ |

| लॉजिक एलिमेंट्स/सेल्सची संख्या | १०१४४० |

| एकूण रॅम बिट्स | ४९७६६४० |

| I/O ची संख्या | २८५ |

| व्होल्टेज - पुरवठा | 0.95V ~ 1.05V |

| माउंटिंग प्रकार | पृष्ठभाग माउंट |

| कार्यशील तापमान | -40°C ~ 100°C (TJ) |

| पॅकेज / केस | 484-BBGA |

| पुरवठादार डिव्हाइस पॅकेज | 484-FBGA (23×23) |

| मूळ उत्पादन क्रमांक | XC7A100 |

नेटवर्क सुरक्षिततेसाठी FPGAs ट्रॅफिक प्रोसेसर म्हणून वापरणे

सुरक्षा साधने (फायरवॉल) कडे जाणारी आणि येणारी रहदारी एकाधिक स्तरांवर एन्क्रिप्ट केली जाते आणि L2 एन्क्रिप्शन/डिक्रिप्शन (MACSec) लिंक लेयर (L2) नेटवर्क नोड्स (स्विच आणि राउटर) वर प्रक्रिया केली जाते.L2 (MAC लेयर) च्या पलीकडे असलेल्या प्रक्रियेमध्ये सामान्यत: सखोल पार्सिंग, L3 टनेल डिक्रिप्शन (IPSec) आणि TCP/UDP रहदारीसह एनक्रिप्टेड SSL रहदारी समाविष्ट असते.पॅकेट प्रक्रियेमध्ये इनकमिंग पॅकेट्सचे पार्सिंग आणि वर्गीकरण आणि उच्च थ्रूपुट (25-400Gb/s) सह मोठ्या रहदारीच्या व्हॉल्यूम (1-20M) वर प्रक्रिया करणे समाविष्ट आहे.

मोठ्या संख्येने संगणकीय संसाधने (कोर) आवश्यक असल्यामुळे, एनपीयू तुलनेने उच्च गती पॅकेट प्रक्रियेसाठी वापरला जाऊ शकतो, परंतु कमी विलंब, उच्च-कार्यक्षमता स्केलेबल ट्रॅफिक प्रक्रिया शक्य नाही कारण ट्रॅफिकवर एमआयपीएस/आरआयएससी कोर वापरून प्रक्रिया केली जाते आणि अशा कोरचे वेळापत्रक तयार केले जाते. त्यांच्या उपलब्धतेवर आधारित कठीण आहे.FPGA-आधारित सुरक्षा उपकरणांचा वापर CPU आणि NPU-आधारित आर्किटेक्चरच्या या मर्यादा प्रभावीपणे दूर करू शकतो.

FPGAs मध्ये ऍप्लिकेशन-स्तरीय सुरक्षा प्रक्रिया

FPGA पुढील पिढीतील फायरवॉलमध्ये इनलाइन सुरक्षा प्रक्रियेसाठी आदर्श आहेत कारण ते उच्च कार्यप्रदर्शन, लवचिकता आणि कमी-विलंब ऑपरेशनची गरज यशस्वीरित्या पूर्ण करतात.याव्यतिरिक्त, FPGAs अनुप्रयोग-स्तरीय सुरक्षा कार्ये देखील लागू करू शकतात, ज्यामुळे संगणकीय संसाधनांची बचत होऊ शकते आणि कार्यप्रदर्शन सुधारू शकते.

FPGAs मध्ये ऍप्लिकेशन सुरक्षा प्रक्रियेची सामान्य उदाहरणे समाविष्ट आहेत

- TTCP ऑफलोड इंजिन

- नियमित अभिव्यक्ती जुळणी

- असममित एनक्रिप्शन (PKI) प्रक्रिया

- TLS प्रक्रिया

FPGAs वापरून पुढील पिढीचे सुरक्षा तंत्रज्ञान

असंख्य विद्यमान असममित अल्गोरिदम क्वांटम संगणकांद्वारे तडजोड करण्यास असुरक्षित आहेत.RSA-2K, RSA-4K, ECC-256, DH आणि ECCDH सारख्या असममित सुरक्षा अल्गोरिदम क्वांटम संगणन तंत्राने सर्वात जास्त प्रभावित होतात.असममित अल्गोरिदम आणि NIST मानकीकरणाची नवीन अंमलबजावणी शोधली जात आहे.

पोस्ट-क्वांटम एन्क्रिप्शनसाठी सध्याच्या प्रस्तावांमध्ये रिंग-ऑन-एरर लर्निंग (आर-एलडब्ल्यूई) पद्धत समाविष्ट आहे

- सार्वजनिक की क्रिप्टोग्राफी (PKC)

- डिजिटल स्वाक्षरी

- की निर्मिती

सार्वजनिक की क्रिप्टोग्राफीच्या प्रस्तावित अंमलबजावणीमध्ये काही सुप्रसिद्ध गणितीय ऑपरेशन्स (TRNG, गॉसियन नॉइज सॅम्पलर, बहुपदी जोड, बायनरी बहुपदी क्वांटिफायर डिव्हिजन, गुणाकार इ.) समाविष्ट आहेत.यापैकी बऱ्याच अल्गोरिदमसाठी FPGA IP उपलब्ध आहे किंवा FPGA बिल्डिंग ब्लॉक्स वापरून कार्यक्षमतेने अंमलात आणले जाऊ शकते, जसे की DSP आणि AI इंजिन (AIE) विद्यमान आणि पुढील-पिढीच्या Xilinx उपकरणांमध्ये.

हे श्वेतपत्र प्रोग्राम करण्यायोग्य आर्किटेक्चर वापरून L2-L7 सुरक्षेच्या अंमलबजावणीचे वर्णन करते जे एंटरप्राइझ नेटवर्क्समध्ये एज/ऍक्सेस नेटवर्क्स आणि नेक्स्ट-जनरेशन फायरवॉल (NGFW) मध्ये सुरक्षा प्रवेगासाठी तैनात केले जाऊ शकते.